-

sa14965.jpg800 x 405 - 38K

sa14965.jpg800 x 405 - 38K

sa14966.jpg800 x 475 - 59K

sa14966.jpg800 x 475 - 59K

sa14967.jpg800 x 417 - 57K

sa14967.jpg800 x 417 - 57K

sa14969.jpg800 x 670 - 58K

sa14969.jpg800 x 670 - 58K

sa14970.jpg800 x 577 - 44K

sa14970.jpg800 x 577 - 44K

sa14971.jpg800 x 627 - 45K

sa14971.jpg800 x 627 - 45K -

Livestream

-

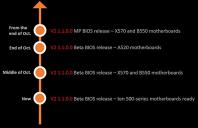

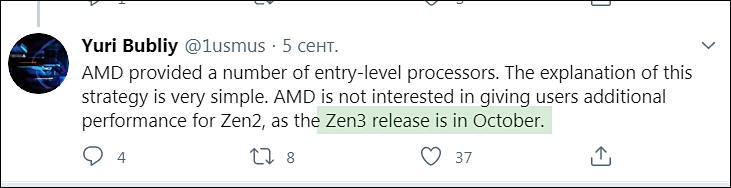

Can be fake, but...

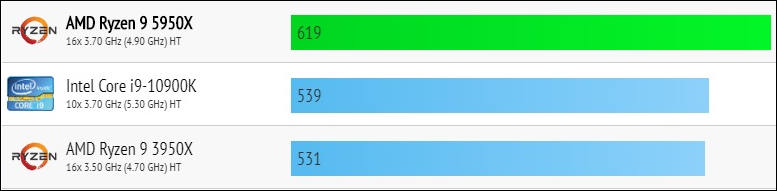

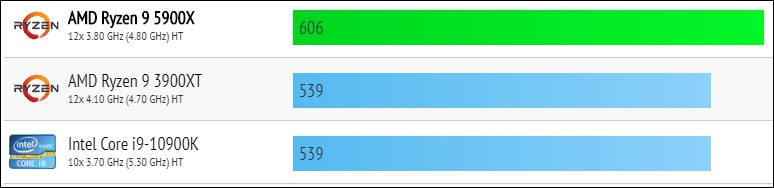

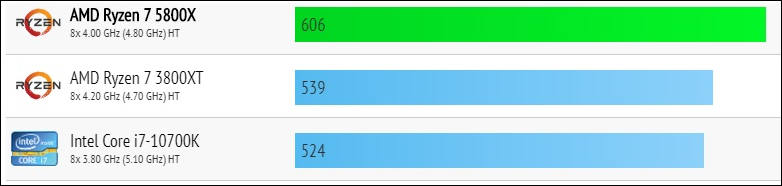

sa14843.jpg777 x 191 - 24K

sa14843.jpg777 x 191 - 24K

sa14844.jpg774 x 188 - 25K

sa14844.jpg774 x 188 - 25K

sa14845.jpg782 x 186 - 25K

sa14845.jpg782 x 186 - 25K -

AMD Ryzen 9 5900X

- 12 cores only

- IPC improvement of up to 20% (around 3% in real life)

- Boost clocks (for short periods) of up to 5 GHz (+300 MHz improvement over the Ryzen 9 3900XT)

- CPU won't be able to offer much higher sustainable all core clock

- 150W TDP (not real consumption, just spec)

- Real consumption will pass 200w for heavy loads during boosts time or overclock

- Price will jump around 15-20% compared to 3900XT

-

Small leak on that happened with Zen 3 original plans to have 4 threads per core

Original Zen 3 design had 4 hyperthreading threads per each core.

But AMD could not make it work good due to thermal issues

As you have more threads you have more parts of each core used and thermal situation becomes worse. In benchmark case CPU can be forced to drop frequency up to 2 times to keep things under control.

In real life of modern 7nm processors they have parts of CPU constantly turned off to limit thermal happening due to leakage. And you can't do it adding too much threads.

Intel also needed to slow down CPU during heavy AVX-512 loads.

sa14775.jpg800 x 563 - 142K

sa14775.jpg800 x 563 - 142K -

AMD can repeat stunt they made with client IO die (part of processor that deal with IO and RAM)

X570 chipset had been actually just mostly rewired IO die from Zen 2 CPU.

X670 chipset can be again just die put on separate board.

-

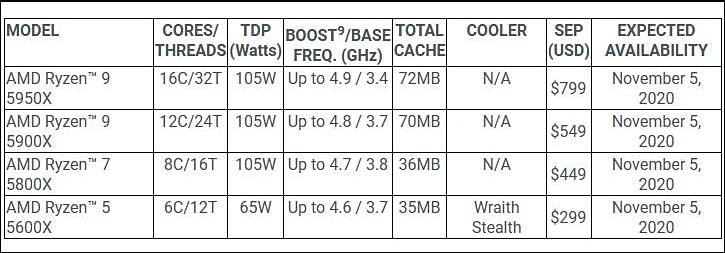

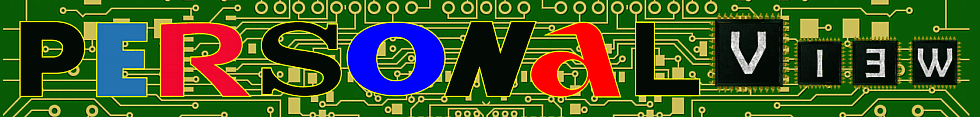

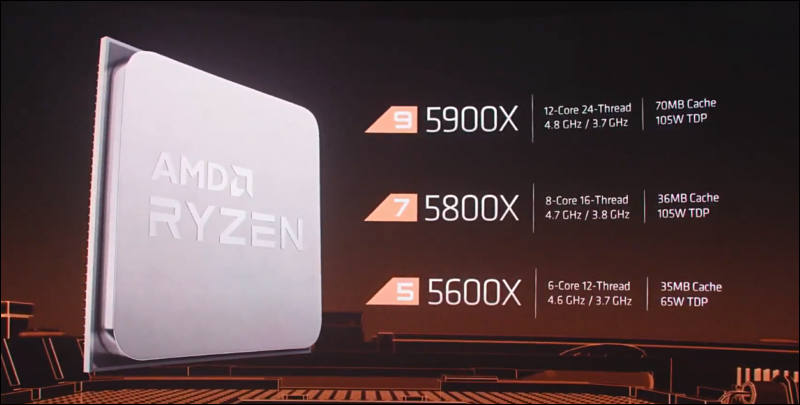

Specific models

- AMD Ryzen 9 5900X - 12 Core

- AMD Ryzen 7 5800X - 8 Core

-

New rumors

- CPUs will have 5xxx names

- It won't be 16 core CPUs (12 cores tops), at least in retail and at initial stages

- AMD can't make too much fully non defective 8 core chiplets now

- Main issue can be horrible situation with 7nm EUV process on TSMC

- AMD had been forced to use this process as 5nm capacity is literally not available

Note that for Zen 2 and Zen 1 number of total fully nondefective chiplets reached 98% after few months, so almost all of lower end CPUs have intentionally disabled cores and even most of the nonconnected chiplets in Threadrippers had been fully functional.

-

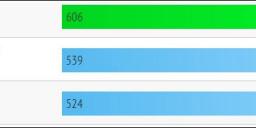

Now all Cores can share larger amounts of cache and add to that latency !!! Plop

-

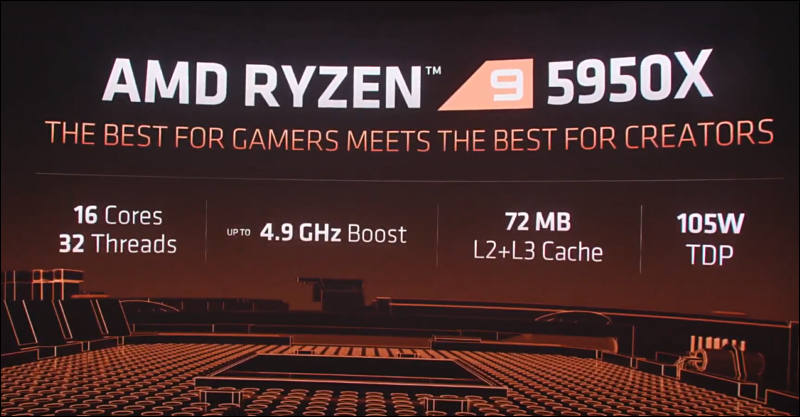

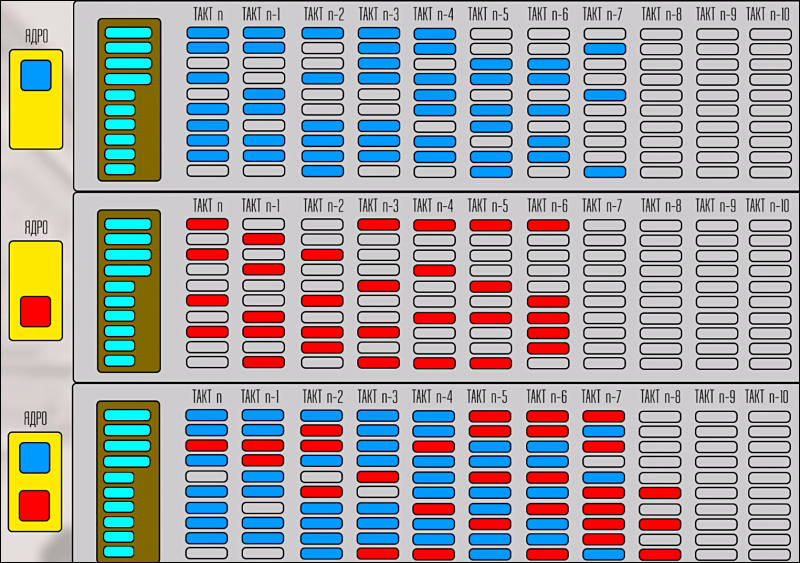

Unlike the previous generation design where each CCD comprised of two CCX's (Core Complexes), the Zen 3 CCD will consist of a single CCX which will feature 8 cores that can run in either a single-thread mode (1T) or a two-thread mode (2T) for up to 16 threads per CCX. Since the chip houses a maximum of two CCDs, the core and thread count will max out at 16 cores and 32 threads which is the same as the existing flagship AM4 desktop CPU, the Ryzen 9 3950X.

Each Zen 3 core will feature 512 KB of L2 cache for a total of 4 MB of L2 cache per CCD. That should equal 8 MB of L2 cache on a dual CCD CPU. Along with the L2 cache, each CCD will also comprise of up to 32 MB of shared L3 cache. For Zen 2, the L3 cache was split between the two CCX's with each CCX having their own separate (Up To) 16 MB cache. The size of the cache remains the same per CCD but now all cores can share a larger number of L3 cache.

https://wccftech.com/amd-zen-3-ryzen-4000-vermeer-cpus-detailed-up-to-16-cores-32-threads/

-

New info tells about 10 core model in lineup

Two chiplet versions will be

- 10 cores, with 6 cores intentionally disabled

- 12 cores, with 4 cores intentionally disabled

- 14 cores, AMD thinking on such version also

- 16 cores, all cores are not disabled by special laser

According to rumors for present TSMC 7nm process and small chiplet size usually 85-90% of chiplets have all 8 cores working and 98% have at least 6 out of 8 working. So, almost all 10 core CPUs and most of 12 core ones are being made by disabling perfectly working cores, just out of marketing purposes.

-

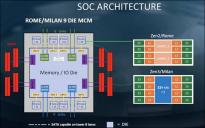

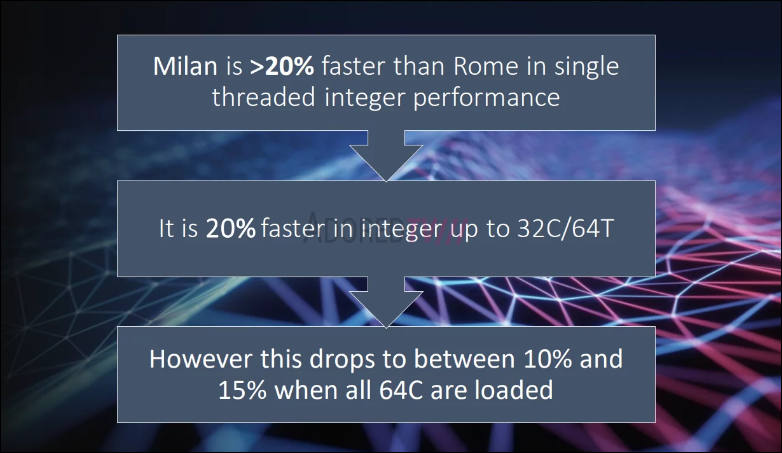

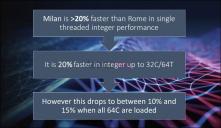

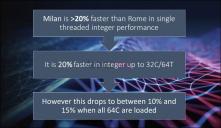

IPC performance increase will be up to + 15% for integer workloads. For EPYC processors with up to 32 cores, AMD wants to achieve a performance increase of + 20% compared to the Rome processors with Zen 2 cores - the single-treaded performance should also increase by + 20%. For the larger EPYC processors with up to 64 cores, AMD expects a performance increase of around 10 to 15%. Apparently, AMD can achieve a higher clock rate for processors with fewer cores, so that the performance increase has a correspondingly higher effect with fewer cores.

Threadripper and Epyc socket will change from Zen 4

With Genoa, AMD is switching from the SP3 to the SP5 platform. The nominal thermal design power ranges from 120 to 240 W, although there are already special models that allow themselves more than 225 W (official TDP limit for normal models). The TDP increases slightly towards the top. AMD gives up platform compatibility with Genoa after three generations. However, due to the use of DDR5 and PCI-Express 5.0 as well as other functions, AMD has no other choice at this point.

sa14239.jpg800 x 500 - 62K

sa14239.jpg800 x 500 - 62K -

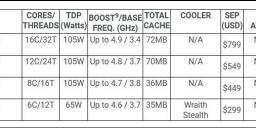

Igor Wallossek's on AMD upcoming Vermeer processor series based on Zen3 architecture.The new information is for the clock speeds, which were decoded from an OPN code Igor was given by the source:

OPN CODE

100-000000059-52_ 48/35 _ Y

The 48 stands for 4.8 GHz boost clock, while 35 means 3.5 GHz base clock. It is still not the final sample, but definitely a faster stepping from the previous report. In June Igor covered first data on the B0 samples which were featuring a boost clock of 4.6 GHz and a base clock of 3.7 GHz.

100-000000059-14_46/37_Y

100-000000059-15_46/37_NEngineering samples mentioned are of course 16 cores and 32 thread CPUs, successors to Ryzen 9 3950X. The new OPN code means that the Vermeer sample is running 100 MHz higher on boost clock compared to 3950X, while the base clock has the same frequency.

Present leaks suggest that benchmarks that use all 16 cores will hsow only 3-7% performance increase comapred to same CPU in Zen 2 lineup.

Thermal constraints no longer allow AMD to increase performance as had been planned.

None of released CPUs will be overclockable (if you do not count extreme nitrogen and such).

-

AMD might in fact skip desktop 4000 series in favor of 5000.

This can make a lot of sense, as the current 4000 series lineup is extremely misleading.

AMD already introduced the series with Renoir-based Ryzen 4000U and Ryzen 4000H models.

-

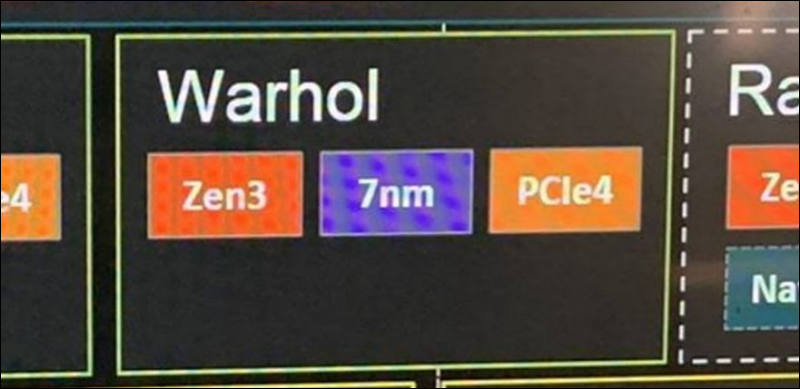

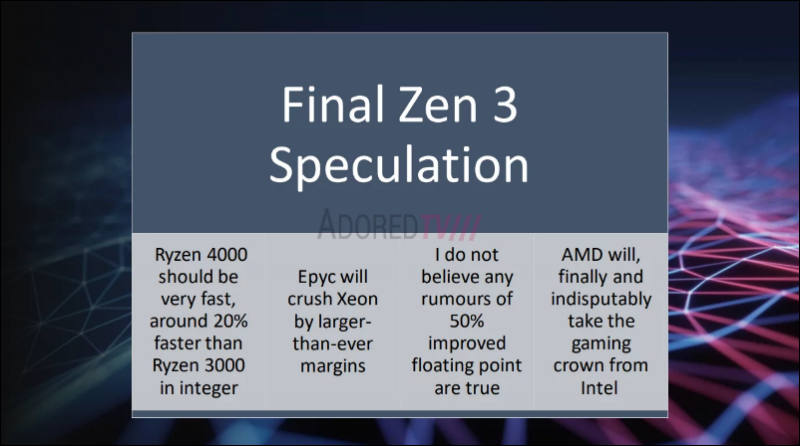

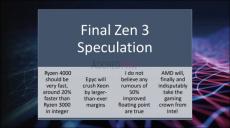

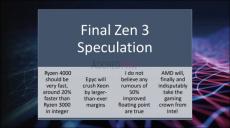

New propaganda from Adored TV

Note that their claims about Zen 2 had been mostly bullshit (I mean performance gains and frequencies).

Here also note that they do not focus on performance per clock.

To get big integer performance advantage they need revolutionary architecture changes.

And note that they are not changing 7nm process much.

Idea of banchamrks can be making special ones that heavily depend on RAM throughput, so making good progress in this regard and comparing you can get needed numbers.

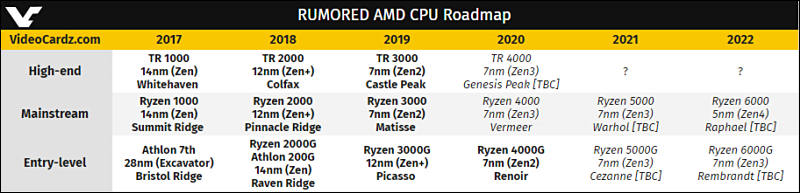

sa13771.jpg782 x 453 - 53K

sa13771.jpg782 x 453 - 53K

sa13772.jpg800 x 446 - 47K

sa13772.jpg800 x 446 - 47K -

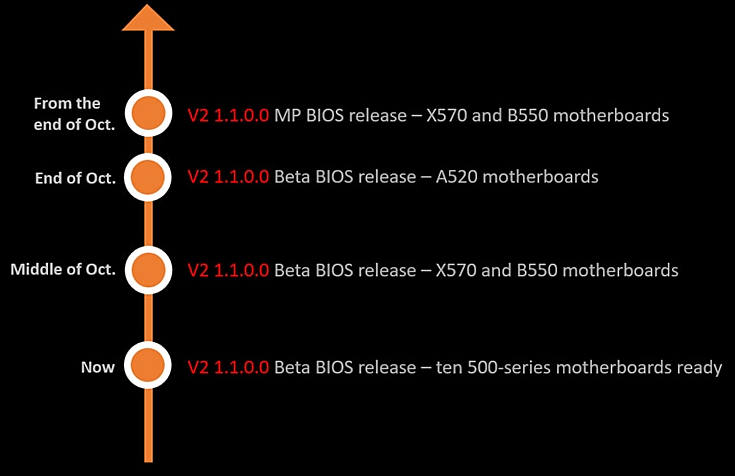

AMD in an official briefing call with us confirmed that the company's "Zen 3" client processors are on-track for launch within 2020. This refutes rumors that "Zen 3" based Ryzen processors had been delayed to 2021 in favor of giving the upcoming Ryzen 3000XT reign over the rest of the year. The call was chaired by AMD's client-segment product managers who were speaking purely in context of their product segment, which is how we deduce that they were referring to "Vermeer" and not [just] "Milan." They were responding to speculation that "Zen 3" has been delayed to 2021, forcing AMD to refresh its existing IP.

In the call, AMD told us that the information about "Zen 3" launching in 2020 is not under embargo, and so here we are. An AMD spokesperson told us that "the rumor on Zen 3 delay is inaccurate." AMD recently also refuted rumors of "Zen 3" being based on 5 nm, by putting out microarchitecture roadmap slides on the occasion of a recent investor relations event, which reaffirmed "Zen 3" as a 7 nm-class microarchitecture.

Back on track.

-

Digitimes, VideoCardz, and RetiredEngineer (twitter) started an intriguing rumor that Ryzen 4000 might end up at 5nm+. Asking around at a reliable place, we have to disappoint some of you as this won't be the case. The Ryzen 4000 series based on Zen 3 core is still at 7nm.

As expected 5nm thing had been idiotic TSMC PR move. As it seems that they don't have 5nm suitable for high powered chips at all now. And wanted to make info clouds for US to make it look that existing 5nm will be suitable for their needs.

Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Categories

- Topics List23,985

- Blog5,725

- General and News1,353

- Hacks and Patches1,152

- ↳ Top Settings33

- ↳ Beginners255

- ↳ Archives402

- ↳ Hacks News and Development56

- Cameras2,363

- ↳ Panasonic993

- ↳ Canon118

- ↳ Sony156

- ↳ Nikon96

- ↳ Pentax and Samsung70

- ↳ Olympus and Fujifilm100

- ↳ Compacts and Camcorders300

- ↳ Smartphones for video97

- ↳ Pro Video Cameras191

- ↳ BlackMagic and other raw cameras115

- Skill1,960

- ↳ Business and distribution66

- ↳ Preparation, scripts and legal38

- ↳ Art149

- ↳ Import, Convert, Exporting291

- ↳ Editors191

- ↳ Effects and stunts115

- ↳ Color grading197

- ↳ Sound and Music280

- ↳ Lighting96

- ↳ Software and storage tips266

- Gear5,420

- ↳ Filters, Adapters, Matte boxes344

- ↳ Lenses1,582

- ↳ Follow focus and gears93

- ↳ Sound499

- ↳ Lighting gear314

- ↳ Camera movement230

- ↳ Gimbals and copters302

- ↳ Rigs and related stuff273

- ↳ Power solutions83

- ↳ Monitors and viewfinders340

- ↳ Tripods and fluid heads139

- ↳ Storage286

- ↳ Computers and studio gear560

- ↳ VR and 3D248

- Showcase1,859

- Marketplace2,834

- Offtopic1,319