It allows to keep PV going, with more focus towards AI, but keeping be one of the few truly independent places.

-

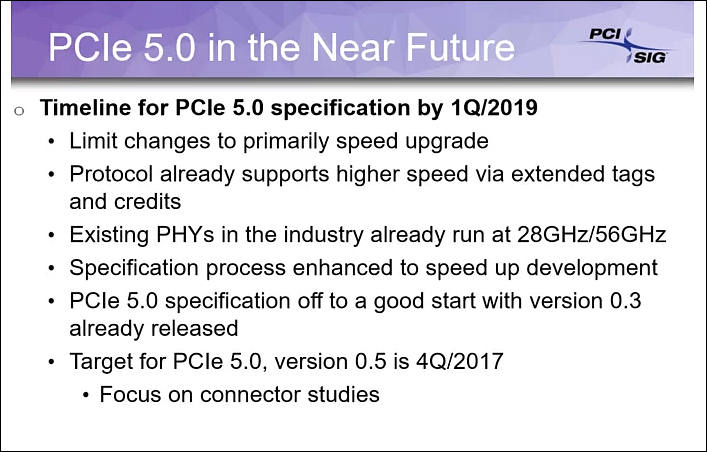

Such situation happened due to extreme delay with PCIe 4.0, and it will be only upcoming AMD 3000 series CPUs that will befirst to implement such standard (even on older motherboards some slots will start to work in it, same as it happened with HDMI after 2200G/2400G introduction).

Rumors in industry are that Apple aims to use PCIe 5.0 in all upcoming 8/16 cores ARM CPUs made for their upcoming iOS based notebooks lines. Of course Thunderbolt via USB-C ports will also greatly benefit from this change with corresponding speed increases.

sa6477.jpg800 x 537 - 50K

sa6477.jpg800 x 537 - 50K

sa6478.jpg707 x 450 - 55K

sa6478.jpg707 x 450 - 55K

sa6479.jpg709 x 452 - 61K

sa6479.jpg709 x 452 - 61K

sa6480.jpg707 x 452 - 62K

sa6480.jpg707 x 452 - 62K -

New TB, new TB, new TB. :). 10 lane TB plug please, for extra wide data rate.

-

The big tradeoff of the higher speeds is that signals won’t travel as far on existing designs. In the days of PCIe 1.0, the spec sent signals as much as 20 inches over traces in mainstream FR4 boards, even passing through two connectors. The fast 4.0 signals will peter out before they travel a foot without going over any connectors.

System makers are sharpening their pencils on the costs of upgrading boards and connectors, adding chips to amplify signals, or redesigning their products to be more compact.

Retimer chips for a full 16-lane full PCIe 4.0 could cost $15 to $25 — if you can find them. Upgrading an adapter card from Megtron-2 to Megtron-4 materials might only add a dollar or so. However, the cost of a similar upgrade for a motherboard is about $100, and if the upgrade is to even higher quality Megtron-6 it would cost about $300.

PCIe 4.0 signals are only travelling three to five inches, said the CEO of PLDA Inc., a designer of PCIe controller cores that came out with 4.0 products three years ago.

“We cannot use FR4. We needed to move to Megtron-6; that’s really clear to me. If you want to get more distance, you need to use retimers, and that’s a bit expensive and tricky.”

“What we have been using for 4.0 and expect to use for 5.0 is twinax cables and firefly connectors, The cost is very low compared to retimers, you can get whatever you want in distance, and the latency is really good.”

The industry has thrived for nearly 18 years on the PCIe mechanicals, but that it’s time for a change.

The GenZ interconnect group is already exploring new designs that put a connector 60 mm closer to a processor.

The 4.0 standard supports FR4 boards for all uses but the longest reaches where retimers are needed, said Yanes. Whether boards will have to move off of FR4 to get the 5.0 speeds “is still part of the discussion … some motherboards may only have a couple of 5.0 slots or attach points.”

So, expect all consumer platforms to have one fast PCIe slot, and may be one extra M.2, al else will be slow same PCIe 3.0.

-

I'm not sure why anyone would want PCIe 4.0 or 5.0, as modern graphics cards are not even saturating PCIe 3.0 16x. Where would anybody need more data throughput (maybe except for servers)?

-

It is simple.

- SSD drives are now limited by PCIe 3.0 x4

- Chipset link is PCIe x4 only now, so copy from one fast SSD to another is limited a lot

- InfiniBand and high speed Ethernet cards, now require x8-x16 slots

This year we will see AMD adding PCIe 4.0 mostly due to first two points.

-

Who needs that much data moved that quickly?

"Office"-User - no.

The usual "high end" gamer - not really.

Videoblogger - also no (I shoot BMD cameras in RAW and it piles up to 1TB quite fast, but even that amount of data is copied bevor I finish my coffee).

More professional production - yes, but they can afford a HEDT like Threadripper or Xeons with plenty of PCIe lanes. Just put NVMe raid cards in 16x slots or the fast network cards.

Don't get me wrong: Progress is good and faster PCIe lanes are a step in the right direction. But the drawbacks (extremly short wires) of PCIe 4.0/5.0 are really bad... and expensive. So, why would anybody throw money at it?

It really does only make sense to have PCIe 4.0/5.0 between the CPU and chipset (as they are really close together anyway) and then have MUCH MORE PCIe 3.0 16x slots on the mainboard.

-

No one asks office user as it is up to department to decide.

Videoblogger - also no (I shoot BMD cameras in RAW and it piles up to 1TB quite fast, but even that amount of data is copied bevor I finish my coffee).

People are different, and not all take during coffee during copy.

On any consumer platform if you use two GPUs you can't use Infiniband anymore.

For example, to edit heavy footage directly on server SSD storage.More professional production - yes, but they can afford a HEDT like Threadripper or Xeons with plenty of PCIe lanes. Just put NVMe raid cards in 16x slots or the fast network cards.

It is consumer products that need PCIe 4.0 and 5.0 the most, exactly as it is total shortage of lines. And yes, you can't do more PCIe lines keeping same price.

They can remove RGB leds, of course, but no sane market manager will do it, as RGB leds sell better :-)It really does only make sense to have PCIe 4.0/5.0 between the CPU and chipset (as they are really close together anyway) and then have MUCH MORE PCIe 3.0 16x slots on the mainboard.

Comment makes no sense. Open any of my recent topics in Storage and Computer and look at real chipset limits and such.

-

Intel plans to have it working in 2021 for server segment, most probably we will see it in consumer segment around 2022-24

sa8397.jpg800 x 414 - 55K

sa8397.jpg800 x 414 - 55K -

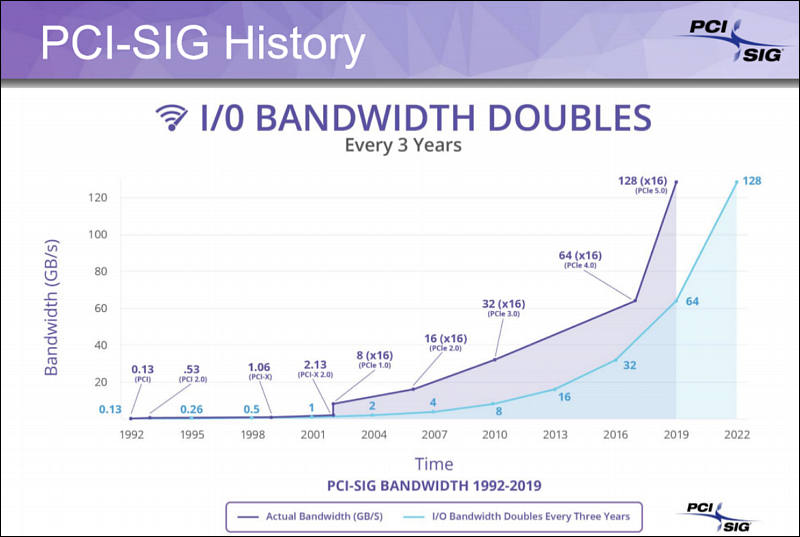

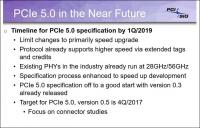

PCI-SIG® today announced the release of PCI Express® (PCIe®) 5.0 specification, reaching 32GT/s transfer rates, while maintaining low power and backwards compatibility with previous technology generations.

“New data-intensive applications are driving demand for unprecedented levels of performance,” said Al Yanes, PCI-SIG Chairman and President. “Completing the PCIe 5.0 specification in 18 months is a major achievement, and it is due to the commitment of our members who worked diligently to evolve PCIe technology to meet the performance needs of the industry. The PCIe architecture will continue to stand as the defacto standard for high performance I/O for the foreseeable future.”

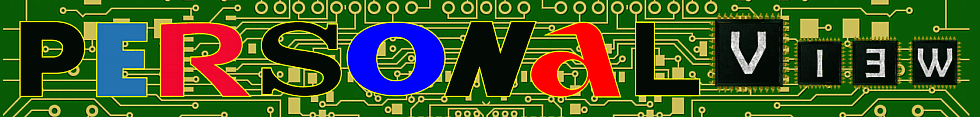

“For 27 years, the PCI-SIG has continually delivered new versions of I/O standards that enable designers to accommodate the never-ending increases in bandwidth required for next generation systems, while preserving investments in prior generation interfaces and software,” noted Nathan Brookwood, research fellow at Insight 64. “Over that period, peak bandwidth has increased from 133 MB/second (for the first 32-bit parallel version) to 32 GB/second (for the V4.0 by16 serial version), a 240X improvement. Wow! The new PCIe 5.0 standard doubles that again to 64 GB/second. Wow2. We have come to take this increased performance for granted, but in reality, it takes a coordinated effort across many members of the PCI-SIG to execute these transitions so seamlessly.”

PCIe 5.0 Specification Highlights

- Delivers 32 GT/s raw bit rate and up to 128 GB/s via x16 configuration

- Leverages and adds to the PCIe 4.0 specification and its support for higher speeds via extended tags and credits

- Implements electrical changes to improve signal integrity and mechanical performance of connectors

- Includes new backwards compatible CEM connector targeted for add-in cards

- Maintains backwards compatibility with PCIe 4.0, 3.x, 2.x and 1.x

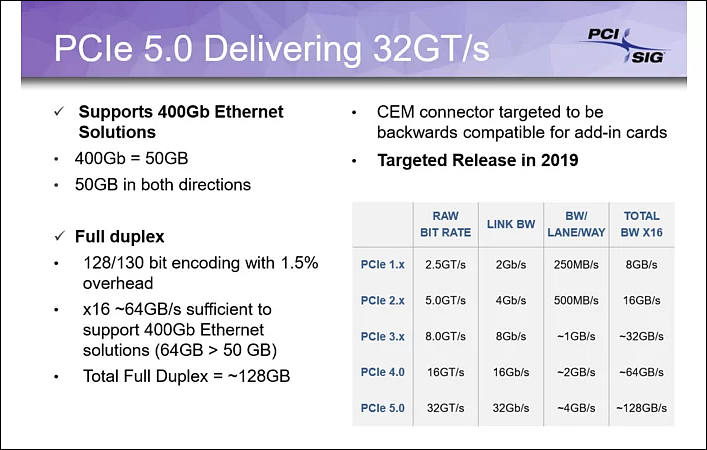

The new specification increases performance in the high-performance markets including artificial intelligence, machine learning, gaming, visual computing, storage and networking.

To learn more about the PCIe 5.0 specification, visit www.pcisig.com. PCI-SIG members can download the full specification here.

-

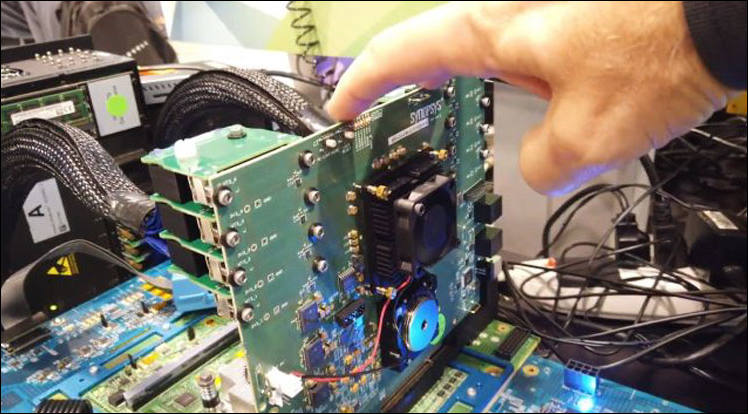

Astera Labs Inc., in collaboration with Synopsys, Inc. (Nasdaq: SNPS), and Intel (Nasdaq: INTC), today announced an industry-first demonstration of a complete PCI Express® (PCIe®) 5.0 system, delivering 32 GT/s speeds for next-generation server workloads. The end-to-end solution showcases system-level multi-vendor interoperability between Intel's PCIe 5.0 test chip, Synopsys' silicon-proven DesignWare® Controller and PHY IP for PCIe 5.0, and Astera Labs' industry-first Smart Retimer SoC for PCIe 5.0. The companies will demonstrate the solution at the PCI-SIG Developers Conference in Taipei, October 28-29.

https://www.design-reuse.com/news/46986/astera-labs-intel-synopsys-pci-express-5-0.html

-

Synopsys, Inc. announced its collaboration with Intel to achieve successful system-level interoperability between the Synopsys DesignWare Controller and PHY IP for PCI Express 5.0 and future Intel Xeon Scalable processors (codename Sapphire Rapids). The full-system interoperability, a key milestone in Synopsys and Intel's ongoing collaboration, enables the ecosystem to confidently use the companies' proven technologies to accelerate development of their PCIe 5.0-based products in high-performance computing and AI applications. The DesignWare IP for PCI Express 5.0 has been licensed over a hundred times by customers across all key market segments, delivering the lowest latency and highest throughput IP compared to other solutions in the industry.

"Synopsys continues to collaborate with industry leaders like Intel to deliver high-quality IP that help designers address the bandwidth, power, area, and latency demands for the new era of high-performance computing systems," said John Koeter, senior vice president of marketing and strategy for IP at Synopsys. "Achieving successful interoperability between Synopsys' DesignWare IP for PCIe 5.0 and Intel Xeon Scalable processors validates that the IP functions as intended with Intel's industry-standard PCIe 5.0 products, accelerating the path to first-silicon success with less risk."

sa15088.jpg748 x 414 - 72K

sa15088.jpg748 x 414 - 72K -

From AMD interview

IC: Can you talk about AMD’s goals with regards to IO and power consumption - we’ve seen AMD deliver PCIe Gen4 in 7nm but the IO die is still based in 12/14nm from Global Foundries. I assume it is a key target for improvements in the future just not this time around?

MP: It’s generational - if you look to the future we drive improvements in every generation. So you will see AMD transition to PCIe Gen 5 and that whole ecosystem. You should expect to hear from us in our next round of generational improvements across both the next-gen core that is in design as well as that next-gen IO and memory controller complex.

https://www.anandtech.com/show/16176/amd-zen-3-an-anandtech-interview-with-cto-mark-papermaster

-

Vendors including Samsung Electronics and Kioxia plan to roll out their respective PCIe Gen5 SSD series for enterprise and datacenter storage in 2022.

-

According to Phison, it is developing a new-generation controller with PCIe 5.0 support, which in theory will provide data transfer rates up to 16 GB / s for NVMe drives. In practice, the figure, of course, will be slightly less.

The manufacturer announced that it has completed the design of the E26 controller test microcircuit based on the 12nm process technology. The company expects the first commercial products based on the new controller series to go on sale in the second half of next year.

sa18383.jpg744 x 445 - 59K

sa18383.jpg744 x 445 - 59K

Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Categories

- Topics List23,992

- Blog5,725

- General and News1,354

- Hacks and Patches1,153

- ↳ Top Settings33

- ↳ Beginners256

- ↳ Archives402

- ↳ Hacks News and Development56

- Cameras2,367

- ↳ Panasonic995

- ↳ Canon118

- ↳ Sony156

- ↳ Nikon96

- ↳ Pentax and Samsung70

- ↳ Olympus and Fujifilm101

- ↳ Compacts and Camcorders300

- ↳ Smartphones for video97

- ↳ Pro Video Cameras191

- ↳ BlackMagic and other raw cameras116

- Skill1,960

- ↳ Business and distribution66

- ↳ Preparation, scripts and legal38

- ↳ Art149

- ↳ Import, Convert, Exporting291

- ↳ Editors191

- ↳ Effects and stunts115

- ↳ Color grading197

- ↳ Sound and Music280

- ↳ Lighting96

- ↳ Software and storage tips266

- Gear5,420

- ↳ Filters, Adapters, Matte boxes344

- ↳ Lenses1,582

- ↳ Follow focus and gears93

- ↳ Sound499

- ↳ Lighting gear314

- ↳ Camera movement230

- ↳ Gimbals and copters302

- ↳ Rigs and related stuff273

- ↳ Power solutions83

- ↳ Monitors and viewfinders340

- ↳ Tripods and fluid heads139

- ↳ Storage286

- ↳ Computers and studio gear560

- ↳ VR and 3D248

- Showcase1,859

- Marketplace2,834

- Offtopic1,320