It allows to keep PV going, with more focus towards AI, but keeping be one of the few truly independent places.

-

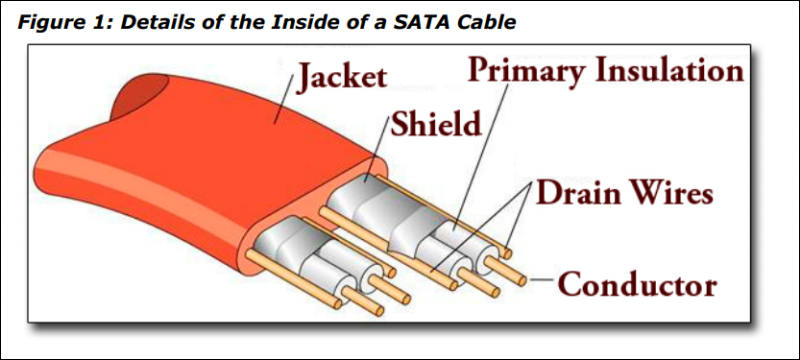

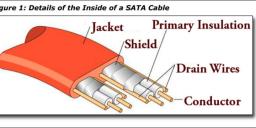

Let's look at SATA 3.0 - native transfer rate is 6.0 Gbit/s; 8b/10b encoding, maximum uncoded transfer rate is 4.8 Gbit/s (600 MB/s).

This is using two differential pairs:

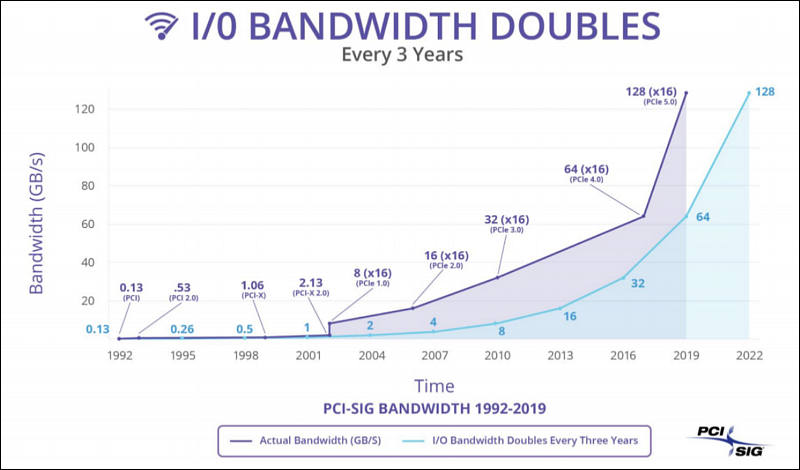

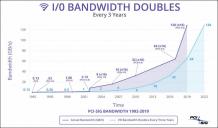

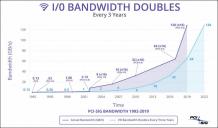

Let's check PCIe that Thunderbolt is using.

PCIe 2.0 standard doubles the transfer rate compared with PCIe 1.0 to 5 GT/s and the per-lane throughput rises from 250 MB/s to 500 MB/s.

PCI Express 3.0 carry a bit rate of 8 gigatransfers per second (GT/s), PCI Express 3.0 upgrades the encoding scheme to 128b/130b from the previous 8b/10b encoding, reducing the bandwidth overhead from 20% of PCI Express 2.0 to approximately 1.54%. PCI Express 3.0's 8 GT/s bit rate effectively delivers 985 MB/s per lane, nearly doubling the lane bandwidth relative to PCI Express 2.0

A x1 connection, the smallest PCIe connection, has one lane made up of four wires.

So, even years ago we had perfectly ready method to get 985 MB/s per lane, could even add internal switch for controller to go into PCIe mode using same wires.

So, decision to stop SATA development had been intentional and not based on any real limits for now, just wanted to drop compatibility layers and simplify interface.

sa6694.jpg800 x 360 - 45K

sa6694.jpg800 x 360 - 45K

sa6692.jpg385 x 509 - 35K

sa6692.jpg385 x 509 - 35K

sa6696.jpg800 x 470 - 44K

sa6696.jpg800 x 470 - 44K -

Interesting fun fact, SATA 3.5 specs released

The maximum exchange rate remained unchanged and froze at 6 Gbit / s. But the developers of the standard promise to increase overall performance and improve integration with other I / O standards.

The first is the technical function of Device Transmit Emphasis for Gen 3 PHY. It allows you to focus on the transmitter, which equates SATA with other I / O solutions when measuring their characteristics. This function should help at the stage of testing and integration of interfaces of new devices.

Secondly, the SATA specifications have a function for determining the ordering of NCQ commands or Defined Ordered NCQ Commands. It allows the host to specify the relationship between the teams in the queue and sets the order in which these commands are processed.

The third new extension in SATA Revision 3.5 is the Command Duration Limit Features. It is designed to reduce delays by allowing the host to define the quality of service categories through more detailed control of the properties of commands.

Looks for me as big warning, such way SATA guys ask for new transfer to keep standard without development.

Without any issues this guys can make speed 4x-8x from current, almots nothing to do.

But it will also mean that value of M2 ports will drop and it'll be much harder to get excess profits for boards with more such ports.

Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Categories

- Topics List23,991

- Blog5,725

- General and News1,354

- Hacks and Patches1,153

- ↳ Top Settings33

- ↳ Beginners256

- ↳ Archives402

- ↳ Hacks News and Development56

- Cameras2,367

- ↳ Panasonic995

- ↳ Canon118

- ↳ Sony156

- ↳ Nikon96

- ↳ Pentax and Samsung70

- ↳ Olympus and Fujifilm101

- ↳ Compacts and Camcorders300

- ↳ Smartphones for video97

- ↳ Pro Video Cameras191

- ↳ BlackMagic and other raw cameras116

- Skill1,960

- ↳ Business and distribution66

- ↳ Preparation, scripts and legal38

- ↳ Art149

- ↳ Import, Convert, Exporting291

- ↳ Editors191

- ↳ Effects and stunts115

- ↳ Color grading197

- ↳ Sound and Music280

- ↳ Lighting96

- ↳ Software and storage tips266

- Gear5,420

- ↳ Filters, Adapters, Matte boxes344

- ↳ Lenses1,582

- ↳ Follow focus and gears93

- ↳ Sound499

- ↳ Lighting gear314

- ↳ Camera movement230

- ↳ Gimbals and copters302

- ↳ Rigs and related stuff273

- ↳ Power solutions83

- ↳ Monitors and viewfinders340

- ↳ Tripods and fluid heads139

- ↳ Storage286

- ↳ Computers and studio gear560

- ↳ VR and 3D248

- Showcase1,859

- Marketplace2,834

- Offtopic1,319